# **Automotive DDR2 SDRAM Data Sheet Addendum**

MT47H128M8 - 16 Meg x 8 x 8 banks MT47H64M16 - 8 Meg x 16 x 8 banks

# **Features**• This addendum provides information to add Auto-

- This addendum provides information to add Automotive Ultra-high Temperature (AUT) option<sup>2</sup> for the data sheet. This addendum does not provide detailed information about the device. Refer to the full data sheet for a complete description of device functionality, operating modes, and specifications for the same Micron part number products.

- $V_{DD} = 1.8V \pm 0.1V$ ,  $V_{DDQ} = 1.8V \pm 0.1V$

- JEDEC-standard 1.8V I/O (SSTL\_18-compatible)

- Differential data strobe (DQS, DQS#) option

- 4*n*-bit prefetch architecture

- Duplicate output strobe (RDQS) option for x8

- DLL to align DQ and DQS transitions with CK

- 8 internal banks for concurrent operation

- Programmable CAS latency (CL)

- Posted CAS additive latency (AL)

- WRITE latency = READ latency 1 <sup>t</sup>CK

- Selectable burst lengths (BL): 4 or 8

- · Adjustable data-output drive strength

- 64ms, 8192-cycle refresh

- On-die termination (ODT)

- RoHS-compliant

- Supports JEDEC clock jitter specification

- PPAP submission

- 8D response time

| Options <sup>1</sup>                                                           | Marking |

|--------------------------------------------------------------------------------|---------|

| <ul> <li>Configuration</li> </ul>                                              |         |

| - 128 Meg x 8 (16 Meg x 8 x 8 banks)                                           | 128M8   |

| <ul> <li>64 Meg x 16 (8 Meg x 16 x 8 banks)</li> </ul>                         | 64M16   |

| • FBGA package (Pb-free) – x16                                                 |         |

| <ul> <li>84-ball FBGA (8mm x 12.5mm)</li> </ul>                                | NF      |

| • FBGA package (Pb-free) – x8                                                  |         |

| <ul> <li>60-ball FBGA (8mm x 10mm)</li> </ul>                                  | SH      |

| • Timing – cycle time                                                          |         |

| -2.5ns @ CL = 5 (DDR2-800)                                                     | -25E    |

| Special option                                                                 |         |

| <ul><li>Standard</li></ul>                                                     | None    |

| <ul> <li>Automotive grade</li> </ul>                                           | A       |

| Operating temperature                                                          |         |

| - Industrial ( $-40^{\circ}$ C $\leq$ T <sub>C</sub> $\leq$ +95 $^{\circ}$ C)  | IT      |

| - Automotive ( $-40^{\circ}$ C $\leq$ T <sub>C</sub> $\leq$ +105 $^{\circ}$ C) | AT      |

| - Ultra-high ( $-40^{\circ}$ C $\leq$ T <sub>C</sub> $\leq$ +125 $^{\circ}$ C) | UT      |

| • Revision                                                                     | :M      |

Notes:

- Not all options listed can be combined to define an offered product. Use the Part Catalog Search on www.micron.com for product offerings and availability.

- 2. UT option use based on automotive usage model. Please contact Micron sales representative if you have questions.

#### **Table 1: Key Timing Parameters**

|             |        | Data Rate (MT/s) |        |        |                      |  |

|-------------|--------|------------------|--------|--------|----------------------|--|

| Speed Grade | CL = 3 | CL = 4           | CL = 5 | CL = 6 | <sup>t</sup> RC (ns) |  |

| -25E        | 400    | 533              | 800    | 800    | 55                   |  |

**Table 2: Addressing**

| Parameter      | 128 Meg x 8          | 64 Meg x 16          |  |  |

|----------------|----------------------|----------------------|--|--|

| Configuration  | 16 Meg x 8 x 8 banks | 8 Meg x 16 x 8 banks |  |  |

| Refresh count  | 8K                   | 8K                   |  |  |

| Row address    | A[13:0] (16K)        | A[12:0] (8K)         |  |  |

| Bank address   | BA[2:0] (8)          | BA[2:0] (8)          |  |  |

| Column address | A[9:0] (1K)          | A[9:0] (1K)          |  |  |

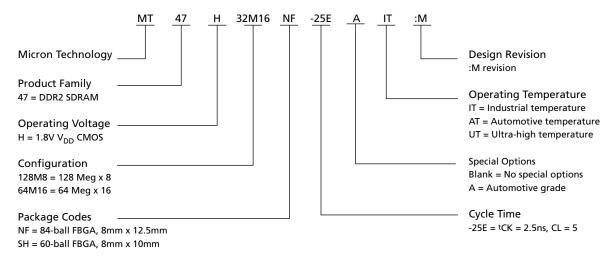

**Figure 1: 1Gb DDR2 Part Numbers**

Note: 1. Not all speeds and configurations are available in all packages.

### **FBGA Part Number System**

Due to space limitations, FBGA-packaged components have an abbreviated part marking that is different from the part number. For a quick conversion of an FBGA code, see the FBGA Part Marking Decoder on Micron's Web site: http://www.micron.com.

#### 1Gb: x8, x16 Automotive DDR2 SDRAM Addendum Important Notes and Warnings

# **Important Notes and Warnings**

Micron Technology, Inc. ("Micron") reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions. This document supersedes and replaces all information supplied prior to the publication hereof. You may not rely on any information set forth in this document if you obtain the product described herein from any unauthorized distributor or other source not authorized by Micron.

Automotive Applications. Products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets. Distributor and customer/distributor shall assume the sole risk and liability for and shall indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting directly or indirectly from any use of non-automotive-grade products in automotive applications. Customer/distributor shall ensure that the terms and conditions of sale between customer/distributor and any customer of distributor/customer (1) state that Micron products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets and (2) require such customer of distributor/customer to indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting from any use of non-automotive-grade products in automotive applications.

Critical Applications. Products are not authorized for use in applications in which failure of the Micron component could result, directly or indirectly in death, personal injury, or severe property or environmental damage ("Critical Applications"). Customer must protect against death, personal injury, and severe property and environmental damage by incorporating safety design measures into customer's applications to ensure that failure of the Micron component will not result in such harms. Should customer or distributor purchase, use, or sell any Micron component for any critical application, customer and distributor shall indemnify and hold harmless Micron and its subsidiaries, subcontractors, and affiliates and the directors, officers, and employees of each against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, or death arising in any way out of such critical application, whether or not Micron or its subsidiaries, subcontractors, or affiliates were negligent in the design, manufacture, or warning of the Micron product.

Customer Responsibility. Customers are responsible for the design, manufacture, and operation of their systems, applications, and products using Micron products. ALL SEMICONDUCTOR PRODUCTS HAVE INHERENT FAIL-URE RATES AND LIMITED USEFUL LIVES. IT IS THE CUSTOMER'S SOLE RESPONSIBILITY TO DETERMINE WHETHER THE MICRON PRODUCT IS SUITABLE AND FIT FOR THE CUSTOMER'S SYSTEM, APPLICATION, OR PRODUCT. Customers must ensure that adequate design, manufacturing, and operating safeguards are included in customer's applications and products to eliminate the risk that personal injury, death, or severe property or environmental damages will result from failure of any semiconductor component.

Limited Warranty. In no event shall Micron be liable for any indirect, incidental, punitive, special or consequential damages (including without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort, warranty, breach of contract or other legal theory, unless explicitly stated in a written agreement executed by Micron's duly authorized representative.

# 1Gb: x8, x16 Automotive DDR2 SDRAM Addendum Functional Description

# **Functional Description**

The DDR2 SDRAM uses a double data rate architecture to achieve high-speed operation. The double data rate architecture is essentially a 4n-prefetch architecture, with an interface designed to transfer two data words per clock cycle at the I/O balls. A single read or write access for the DDR2 SDRAM effectively consists of a single 4n-bit-wide, one-clock-cycle data transfer at the internal DRAM core and four corresponding n-bit-wide, one-half-clock-cycle data transfers at the I/O balls.

A bidirectional data strobe (DQS, DQS#) is transmitted externally, along with data, for use in data capture at the receiver. DQS is a strobe transmitted by the DDR2 SDRAM during READs and by the memory controller during WRITEs. DQS is edge-aligned with data for READs and center-aligned with data for WRITEs. The x16 offering has two data strobes, one for the lower byte (LDQS, LDQS#) and one for the upper byte (UDQS, UDQS#).

The DDR2 SDRAM operates from a differential clock (CK and CK#); the crossing of CK going HIGH and CK# going LOW will be referred to as the positive edge of CK. Commands (address and control signals) are registered at every positive edge of CK. Input data is registered on both edges of DQS, and output data is referenced to both edges of DQS as well as to both edges of CK.

Read and write accesses to the DDR2 SDRAM are burst-oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVATE command, which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVATE command are used to select the bank and row to be accessed. The address bits registered coincident with the READ or WRITE command are used to select the bank and the starting column location for the burst access.

The DDR2 SDRAM provides for programmable read or write burst lengths of four or eight locations. DDR2 SDRAM supports interrupting a burst read of eight with another read or a burst write of eight with another write. An auto precharge function may be enabled to provide a self-timed row precharge that is initiated at the end of the burst access.

As with standard DDR SDRAM, the pipelined, multibank architecture of DDR2 SDRAM enables concurrent operation, thereby providing high, effective bandwidth by hiding row precharge and activation time.

A self refresh mode is provided, along with a power-saving, power-down mode.

All inputs are compatible with the JEDEC standard for SSTL\_18. All full drive-strength outputs are SSTL\_18-compatible.

# **Automotive Industrial Temperature (AIT)**

The industrial temperature (AIT) option, if offered, the case temperature cannot be less than –40°C or greater than +95°C. JEDEC specifications require the refresh rate to double when  $T_{\rm C}$  exceeds +85°C; this also requires use of the high-temperature self refresh option. Additionally, ODT resistance, the input/output impedance, and  $I_{\rm DD}$  values must be derated when  $T_{\rm C}$  is < 0°C or > +85°C.

# 1Gb: x8, x16 Automotive DDR2 SDRAM Addendum Functional Description

#### **Automotive-grade Automotive Temperature (AAT)**

The automotive-grade automotive temperature (AAT) option, if offered, the case temperature cannot be less than  $-40^{\circ}\text{C}$  or greater than  $+105^{\circ}\text{C}$ . JEDEC specifications require the refresh rate to double when  $T_{\text{C}}$  exceeds  $+85^{\circ}\text{C}$ ; this also requires use of the high-temperature self refresh option. Additionally, ODT resistance, the input/output impedance, and  $I_{\text{DD}}$  values must be derated when  $T_{\text{C}}$  is  $<0^{\circ}\text{C}$  or  $>+85^{\circ}\text{C}$ .

### **Automotive Ultra-high Temperature (AUT)**

The automotive ultra-high temperature (AUT) option, if offered, the case temperature cannot be less than –40°C or greater than +125°C. JEDEC specifications require the refresh rate to double when  $T_{C}$  exceeds +85°C; this also requires use of the high-temperature auto refresh mode. When Tc > +105C, the refresh rate must be increased to 8X. Self refresh mode is not available for Tc >+105°C. . Additionally, ODT resistance, the input/output impedance, and  $I_{DD}$  values must be derated when  $T_{C}$  is < 0°C or > +85°C.

#### **General Notes**

- The functionality and the timing specifications discussed in this data sheet are for the DLL-enabled mode of operation.

- Throughout the data sheet, the various figures and text refer to DQs as "DQ." The DQ term is to be interpreted as any and all DQ collectively, unless specifically stated otherwise. Additionally, the x16 is divided into 2 bytes: the lower byte and the upper byte. For the lower byte (DQ0–DQ7), DM refers to LDM and DQS refers to LDQS. For the upper byte (DQ8–DQ15), DM refers to UDM and DQS refers to UDQS.

- A x16 device's DQ bus is comprised of two bytes. If only one of the bytes needs to be used, use the lower byte for data transfers and terminate the upper byte as noted:

- Connect UDQS to ground via 1kΩ\* resistor

- Connect UDQS# to  $V_{DD}$  via  $1k\Omega^*$  resistor

- Connect UDM to  $V_{DD}$  via  $1k\Omega^*$  resistor

- Connect DQ[15:8] individually to either  $V_{SS}$  or  $V_{DD}$  via  $1k\Omega^*$  resistors, or float DQ[15:8].

- \*If ODT is used,  $1k\Omega$  resistor should be changed to 4x that of the selected ODT.

- Complete functionality is described throughout the document, and any page or diagram may have been simplified to convey a topic and may not be inclusive of all requirements.

- Any specific requirement takes precedence over a general statement.

### 1Gb: x8, x16 Automotive DDR2 SDRAM Addendum **Electrical Specifications - Absolute Ratings**

# **Electrical Specifications – Absolute Ratings**

Stresses greater than those listed may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

**Table 3: Absolute Maximum DC Ratings**

| Parameter                                                                                           | Symbol                             | Min  | Max | Units | Notes |

|-----------------------------------------------------------------------------------------------------|------------------------------------|------|-----|-------|-------|

| $V_{DD}$ supply voltage relative to $V_{SS}$                                                        | $V_{DD}$                           | -1.0 | 2.3 | V     | 1     |

| $V_{DDQ}$ supply voltage relative to $V_{SSQ}$                                                      | $V_{DDQ}$                          | -0.5 | 2.3 | V     | 1, 2  |

| $V_{DDL}$ supply voltage relative to $V_{SSL}$                                                      | $V_{DDL}$                          | -0.5 | 2.3 | V     | 1     |

| Voltage on any ball relative to V <sub>SS</sub>                                                     | V <sub>IN</sub> , V <sub>OUT</sub> | -0.5 | 2.3 | V     | 3     |

| Input leakage current; any input $0V \le V_{IN} \le V_{DD}$ ; all other balls not under test = $0V$ | I <sub>I</sub>                     | -5   | 5   | μΑ    |       |

| Output leakage current; $0V \le V_{OUT} \le V_{DDQ}$ ; DQ and ODT disabled                          | I <sub>OZ</sub>                    | -5   | 5   | μΑ    |       |

| $V_{REF}$ leakage current; $V_{REF}$ = Valid $V_{REF}$ level                                        | I <sub>VREF</sub>                  | -2   | 2   | μΑ    |       |

- Notes: 1. V<sub>DD</sub>, V<sub>DDO</sub>, and V<sub>DDL</sub> must be within 300mV of each other at all times; this is not required when power is ramping down.

- 2.  $V_{REF} \le 0.6 \times V_{DDQ}$ ; however,  $V_{REF}$  may be  $\ge V_{DDQ}$  provided that  $V_{REF} \le 300$  mV.

- 3. Voltage on any I/O may not exceed voltage on V<sub>DDO</sub>.

## **Temperature and Thermal Impedance**

It is imperative that the DDR2 SDRAM device's temperature specifications, shown in Table 4 (page 7), be maintained in order to ensure the junction temperature is in the proper operating range to meet data sheet specifications. An important step in maintaining the proper junction temperature is using the device's thermal impedances correctly. The thermal impedances are listed in Table 5 (page 7) for the applicable and available die revision and packages.

Incorrectly using thermal impedances can produce significant errors. Read Micron technical note TN-00-08, "Thermal Applications" prior to using the thermal impedances listed in Table 5. For designs that are expected to last several years and require the flexibility to use several DRAM die shrinks, consider using final target theta values (rather than existing values) to account for increased thermal impedances from the die size reduction.

The DDR2 SDRAM device's safe junction temperature range can be maintained when the T<sub>C</sub> specification is not exceeded. In applications where the device's ambient temperature is too high, use of forced air and/or heat sinks may be required in order to satisfy the case temperature specifications.

**Table 4: Temperature Limits**

| Parameter                              | Symbol           | Min | Max | Units | Notes |

|----------------------------------------|------------------|-----|-----|-------|-------|

| Storage temperature                    | T <sub>STG</sub> | -55 | 150 | °C    | 1     |

| Operating temperature: commercial (CT) | T <sub>C</sub>   | 0   | 85  | °C    | 2, 3  |

| Operating temperature: industrial (IT) | T <sub>C</sub>   | -40 | 95  | °C    | 2, 3, |

| Operating temperature: automotive (AT) | T <sub>C</sub>   | -40 | 105 | °C    | 2, 3, |

| Operating temperature: ultra-high (UT) | T <sub>C</sub>   | -40 | 125 | °C    | 2,3,4 |

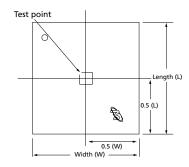

- Notes: 1. MAX storage case temperature T<sub>STG</sub> is measured in the center of the package, as shown in Figure 2. This case temperature limit is allowed to be exceeded briefly during package reflow, as noted in Micron technical note TN-00-15, "Recommended Soldering Parame-

- 2. MAX operating case temperature T<sub>C</sub> is measured in the center of the package, as shown in Figure 2.

- 3. Device functionality is not guaranteed if the device exceeds maximum T<sub>C</sub> during opera-

- 4. Ultra-high temperature use based on automotive usage model. Please contact Micron sales representative if you have questions.

**Figure 2: Example Temperature Test Point Location**

Lmm x Wmm FBGA

**Table 5: Thermal Impedance**

|                     |         | Substrate         | θ JA (°C/W)    | θ JA (°C/W)    | θ JA (°C/W)    |             |                                      |

|---------------------|---------|-------------------|----------------|----------------|----------------|-------------|--------------------------------------|

| <b>Die Revision</b> | Package | (pcb)             | Airflow = 0m/s | Airflow = 1m/s | Airflow = 2m/s | θ JB (°C/W) | θ <b>JC</b> (° <b>C</b> / <b>W</b> ) |

|                     | 60-ball | Low Conductivity  | 85.4           | 70.6           | 64.5           | 42.8        | 11.7                                 |

| M <sup>1</sup>      | 00-ball | High Conductivity | 63.2           | 56.1           | 52.8           | 42.0        | 11.7                                 |

| IVI                 | 84-ball | Low Conductivity  | 80.8           | 67.0           | 61.6           | 44.7        | 11.7                                 |

|                     | 04-ball | High Conductivity | 59.7           | 53.3           | 50.7           | 44.7        | 11.7                                 |

Note: 1. Thermal resistance data is based on a number of samples from multiple lots and should be viewed as a typical number.

# **Electrical Specifications – IDD Parameters**

### **IDD** Specifications and Conditions

**Table 6: General IDD Parameters**

| I <sub>DD</sub> Parameters                      | -25E                                   | Units           |

|-------------------------------------------------|----------------------------------------|-----------------|

| CL (I <sub>DD</sub> )                           | 5                                      | <sup>t</sup> CK |

| <sup>t</sup> RCD (I <sub>DD</sub> )             | 12.5                                   | ns              |

| <sup>t</sup> RC (I <sub>DD</sub> )              | 57.5                                   | ns              |

| <sup>t</sup> RRD (I <sub>DD</sub> ) - x8 (1KB)  | 7.5                                    | ns              |

| <sup>t</sup> RRD (I <sub>DD</sub> ) - x16 (2KB) | 10                                     | ns              |

| <sup>t</sup> CK (I <sub>DD</sub> )              | 2.5                                    | ns              |

| <sup>t</sup> RAS MIN (I <sub>DD</sub> )         | 45                                     | ns              |

| <sup>t</sup> RAS MAX (I <sub>DD</sub> )         | 70,000                                 | ns              |

| <sup>t</sup> RP (I <sub>DD</sub> )              | 12.5                                   | ns              |

| <sup>t</sup> RFC (I <sub>DD</sub> - 256Mb)      | 75                                     | ns              |

| <sup>t</sup> RFC (I <sub>DD</sub> - 512Mb)      | 105                                    | ns              |

| <sup>t</sup> RFC (I <sub>DD</sub> - 1Gb)        | 127.5                                  | ns              |

| <sup>t</sup> RFC (I <sub>DD</sub> - 2Gb)        | 197.5                                  | ns              |

| <sup>t</sup> FAW (I <sub>DD</sub> ) - x8 (1KB)  | Defined by pattern in Table 7 (page 8) | ns              |

| <sup>t</sup> FAW (I <sub>DD</sub> ) - x16 (2KB) | Defined by pattern in Table 7 (page 8) | ns              |

## **IDD7** Conditions

The detailed timings are shown below for  $I_{DD7}$ . Where general  $I_{DD}$  parameters in Table 6 (page 8) conflict with pattern requirements of Table 7, then Table 7 requirements take precedence.

**Table 7: IDD7 Timing Patterns (8-Bank Interleave READ Operation)**

| Speed<br>Grade                           | I <sub>DD7</sub> Timing Patterns                                                                |  |  |  |  |

|------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| Timing patterns for 8-bank x4/x8 devices |                                                                                                 |  |  |  |  |

| -25E                                     | A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D D A4 RA4 D A5 RA5 D A6 RA6 D A7 RA7 D D D                 |  |  |  |  |

| Timing patterns for 8-bank x16 devices   |                                                                                                 |  |  |  |  |

| -25E                                     | A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D D A4 RA4 D D A5 RA5 D D A6 RA6 D D A7 RA7 D D D D |  |  |  |  |

Notes: 1. A = active; RA = read auto precharge; D = deselect.

- 2. All banks are being interleaved at  ${}^{t}RC$  ( $I_{DD}$ ) without violating  ${}^{t}RRD$  ( $I_{DD}$ ) using a BL = 4.

- 3. Control and address bus inputs are stable during deselects.

# Table 8: DDR2 I<sub>DD</sub> Specifications and Conditions (Die Revision M)

Notes: 1-7 apply to the entire table

| Parameter/Condition                                                                                                                                                                                                                                                                                                 | Symbol             | Configuration         | -25E | Units |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|------|-------|

| Operating one bank active-                                                                                                                                                                                                                                                                                          | I <sub>DD0</sub>   | х8                    | 65   | mA    |

| <b>precharge current:</b> ${}^{t}CK = {}^{t}CK (I_{DD})$ , ${}^{t}RC = {}^{t}RC (I_{DD})$ , ${}^{t}RAS = {}^{t}RAS MIN (I_{DD})$ ; CKE is HIGH, CS# is HIGH between valid commands; Address bus inputs are switching; Data bus inputs are switching                                                                 |                    | x16                   | 80   |       |

| Operating one bank active-read-precharge current: $I_{OUT} = 0 \text{mA}$ ;                                                                                                                                                                                                                                         | $I_{DD1}$          | x8                    | 75   | mA    |

| BL = 4, CL = CL ( $I_{DD}$ ), AL = 0; ${}^{t}CK = {}^{t}CK$ ( $I_{DD}$ ), ${}^{t}RC = {}^{t}RC$ ( $I_{DD}$ ), ${}^{t}RAS = {}^{t}RAS$ MIN ( $I_{DD}$ ), ${}^{t}RCD = {}^{t}RCD$ ( $I_{DD}$ ); CKE is HIGH, CS# is HIGH between valid commands; Address bus inputs are switching; Data pattern is same as $I_{DD4W}$ |                    | x16                   | 95   |       |

| <b>Precharge power-down current:</b> All banks idle; ${}^{t}CK = {}^{t}CK$ ( $I_{DD}$ ); CKE is LOW; Other control and address bus inputs are stable; Data bus inputs are floating                                                                                                                                  | I <sub>DD2P</sub>  | x8, x16               | 10   | mA    |

| Precharge quiet standby                                                                                                                                                                                                                                                                                             | I <sub>DD2Q</sub>  | x8                    | 24   | mA    |

| <b>current:</b> All banks idle; <sup>t</sup> CK = <sup>t</sup> CK (I <sub>DD</sub> ); CKE is HIGH, CS# is HIGH; Other control and address bus inputs are stable; Data bus inputs are floating                                                                                                                       |                    | x16                   | 26   |       |

| <b>Precharge standby current:</b> All banks idle; ${}^{t}CK = {}^{t}CK (I_{DD})$ ; CKE is                                                                                                                                                                                                                           | I <sub>DD2N</sub>  | x8                    | 28   | mA    |

| HIGH, CS# is HIGH; Other control and address bus inputs are switching; Data bus inputs are switching                                                                                                                                                                                                                |                    | x16                   | 30   |       |

| <b>Active power-down current:</b> All banks open; ${}^{t}CK = {}^{t}CK (I_{DD})$ ; CKE is LOW; Other control and address bus inputs are stable; Data bus in-                                                                                                                                                        | I <sub>DD3Pf</sub> | Fast exit<br>MR12 = 0 | 30   | mA    |

| puts are floating                                                                                                                                                                                                                                                                                                   | I <sub>DD3Ps</sub> | Slow exit<br>MR12 = 1 | 20   |       |

| <b>Active standby current:</b> All banks open; <sup>t</sup> CK = <sup>t</sup> CK (I <sub>DD</sub> ), <sup>t</sup> RAS =                                                                                                                                                                                             | I <sub>DD3N</sub>  | x8                    | 33   | mA    |

| ${}^{t}RAS\ MAX\ (I_{DD}),\ {}^{t}RP={}^{t}RP\ (I_{DD});\ CKE\ is\ HIGH,\ CS\#\ is\ HIGH\ between\ valid\ commands;\ Other\ control\ and\ address\ bus\ inputs\ are\ switching;\ Data\ bus\ inputs\ are\ switching$                                                                                                 |                    | x16                   | 38   |       |

| Operating burst write current: All banks open, continuous burst                                                                                                                                                                                                                                                     | I <sub>DD4W</sub>  | x8                    | 125  | mA    |

| writes; BL = 4, CL = CL ( $I_{DD}$ ), AL = 0; ${}^{t}CK = {}^{t}CK (I_{DD})$ , ${}^{t}RAS = {}^{t}RAS$ MAX ( $I_{DD}$ ), ${}^{t}RP = {}^{t}RP (I_{DD})$ ; CKE is HIGH, CS# is HIGH between valid commands; Address bus inputs are switching; Data bus inputs are switching                                          |                    | x16                   | 160  |       |

| Operating burst read current: All banks open, continuous burst                                                                                                                                                                                                                                                      | I <sub>DD4R</sub>  | x8                    | 120  | mA    |

| reads, $I_{OUT}$ = 0mA; BL = 4, CL = CL ( $I_{DD}$ ), AL = 0; ${}^{t}CK$ = ${}^{t}CK$ ( $I_{DD}$ ), ${}^{t}RAS$ = ${}^{t}RAS$ MAX ( $I_{DD}$ ), ${}^{t}RP$ = ${}^{t}RP$ ( $I_{DD}$ ); CKE is HIGH, CS# is HIGH between valid commands; Address bus inputs are switching; Data bus inputs are switching              |                    | x16                   | 150  |       |

| <b>Burst refresh current:</b> <sup>t</sup> CK = <sup>t</sup> CK (I <sub>DD</sub> ); REFRESH command at every                                                                                                                                                                                                        | I <sub>DD5</sub>   | x8                    | 155  | mA    |

| <sup>t</sup> RFC (I <sub>DD</sub> ) interval; CKE is HIGH, CS# is HIGH between valid commands; Other control and address bus inputs are switching; Data bus inputs are switching                                                                                                                                    |                    | x16                   | 160  |       |

| <b>Self refresh current:</b> CK and CK# at 0V; CKE ≤ 0.2V; Other control and address bus inputs are floating; Data bus inputs are floating                                                                                                                                                                          | I <sub>DD6</sub>   | x8, x16               | 7    | mA    |

#### Table 8: DDR2 IDD Specifications and Conditions (Die Revision M) (Continued)

Notes: 1-7 apply to the entire table

| Parameter/Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Symbol           | Configuration | -25E | Units |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|------|-------|

| Operating bank interleave read                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I <sub>DD7</sub> | x8            | 210  | mA    |

| <b>current:</b> All bank interleaving reads, $I_{OUT} = 0$ mA; $BL = 4$ , $CL = CL$ ( $I_{DD}$ ), $AL = {}^{t}RCD$ ( $I_{DD}$ ) - 1 × ${}^{t}CK$ ( $I_{DD}$ ); ${}^{t}CK = {}^{t}CK$ ( $I_{DD}$ ), ${}^{t}RC = {}^{t}RC$ ( $I_{DD}$ ), ${}^{t}RRD = {}^{t}RRD$ ( $I_{DD}$ ), ${}^{t}RCD = {}^{t}RCD$ ( $I_{DD}$ ); $CKE$ is HIGH, $CS\#$ is HIGH between valid commands; Address bus inputs are stable during deselects; Data bus inputs are switching; See IDD7 Conditions for details |                  | x16           | 260  |       |

Notes

- I<sub>DD</sub> specifications are tested after the device is properly initialized. 0°C ≤ T<sub>C</sub> ≤ +85°C.

- 2.  $V_{DD} = +1.8V \pm 0.1V$ ,  $V_{DDQ} = +1.8V \pm 0.1V$ ,  $V_{DDL} = +1.8V \pm 0.1V$ ,  $V_{REF} = V_{DDQ}/2$ .

- 3. I<sub>DD</sub> parameters are specified with ODT disabled.

- 4. Data bus consists of DQ, DM, DQS, DQS#, RDQS#, LDQS, LDQS#, UDQS, and UDQS#. IDD values must be met with all combinations of EMR bits 10 and 11.

- 5. Definitions for IDD conditions:

**LOW**  $V_{IN} \le V_{IL(AC)max}$ **HIGH**  $V_{IN} \ge V_{IH(AC)min}$

**Stable** Inputs stable at a HIGH or LOW level

**Floating** Inputs at  $V_{REF} = V_{DDQ}/2$

Switching Inputs changing between HIGH and LOW every other clock cycle (once per

two clocks) for address and control signals

Switching Inputs changing between HIGH and LOW every other data transfer (once

per clock) for DQ signals, not including masks or strobes

- 6.  $I_{DD1}$ ,  $I_{DD4R}$ , and  $I_{DD7}$  require A12 in EMR to be enabled during testing.

- 7. The following  $I_{DD}$  values must be derated ( $I_{DD}$  limits increase) on IT-option and AT-option devices when operated outside of the range  $0^{\circ}C \le T_{C} \le 85^{\circ}C$ :

When I<sub>DD2P</sub> and I<sub>DD3P(SLOW)</sub> must be derated by 4%; I<sub>DD4R</sub> and I<sub>DD4W</sub> must be derat-

$T_C \le 0^{\circ}C$  ed by 2%; and  $I_{DD6}$  and  $I_{DD7}$  must be derated by 7%

**When**  $I_{DD0}$ ,  $I_{DD1}$ ,  $I_{DD2N}$ ,  $I_{DD2Q}$ ,  $I_{DD3N}$ ,  $I_{DD3P(FAST)}$ ,  $I_{DD4R}$ ,  $I_{DD4W}$ , and  $I_{DD5}$  must be derated by 2%;  $I_{DD3P}$  must be derated by 20%;  $I_{DD3P(SLOW)}$  must be derated by

30%; and I<sub>DD6</sub> must be derated by 80% (I<sub>DD6</sub> will increase by this amount if

$T_C$  < 85°C and the 2X refresh option is still enabled)

**When** 8X refresh is required, self-refresh mode is not available.

T<sub>C</sub> ≥105°C

#### **Table 9: AC Operating Specifications and Conditions**

Not all speed grades listed may be supported for this device; refer to the title page for speeds supported; Notes: 1–5 apply to the entire table;

|              | AC Characteristic                  |                                                                                                                                                                                                                                                              | -2!                                                                                      | 5E                                                                                 |                 |                   |

|--------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------|-------------------|

|              | Parameter                          | Symbol                                                                                                                                                                                                                                                       | Min                                                                                      | Мах                                                                                | Units           | Notes             |

|              | Clock CL = 6                       | tCK (avg)                                                                                                                                                                                                                                                    | 2.5                                                                                      | 8.0                                                                                | ns              | 6, 7, 8,          |

|              | cycle time CL = 5                  | tCK (avg)                                                                                                                                                                                                                                                    | 2.5                                                                                      | 8.0                                                                                |                 | 9                 |

|              | CL = 4                             | tCK (avg)                                                                                                                                                                                                                                                    | 3.75                                                                                     | 8.0                                                                                |                 |                   |

|              | CL = 3                             | tCK (avg)                                                                                                                                                                                                                                                    | 5.0                                                                                      | 8.0                                                                                |                 |                   |

|              | CK high-level width                | tCH (avg)                                                                                                                                                                                                                                                    | 0.48                                                                                     | 0.52                                                                               | <sup>t</sup> CK | 10                |

| J            | CK low-level width                 | <sup>t</sup> CL (avg)                                                                                                                                                                                                                                        | 0.48                                                                                     | 0.52                                                                               | <sup>t</sup> CK |                   |

| Clock        | Half clock period                  | tHP                                                                                                                                                                                                                                                          | MIN = lesser o<br>MAX                                                                    |                                                                                    | ps              | 11                |

|              | Absolute <sup>t</sup> CK           | <sup>t</sup> CK (abs)                                                                                                                                                                                                                                        | $MIN = {}^{t}CK (AVG) N$ $MAX = {}^{t}CK (AVG) M$                                        |                                                                                    | ps              |                   |

|              | Absolute CK<br>high-level width    | <sup>t</sup> CH (abs)                                                                                                                                                                                                                                        | $MIN = {}^{t}CK (AVG) MIN \times {}^{t}CH$<br>$MAX = {}^{t}CK (AVG) MAX \times {}^{t}CH$ | I (AVG) MIN + <sup>t</sup> JITdty (MIN)<br>I (AVG) MAX + <sup>t</sup> JITdty (MAX) | ps              |                   |

|              | Absolute CK<br>low-level width     | th $^{t}CL$ (abs) $MIN = {}^{t}CK$ (AVG) $MIN \times {}^{t}CL$ (AVG) $MIN + {}^{t}JITdty$ (MIN the MAX = ${}^{t}CK$ (AVG) $MAX \times {}^{t}CL$ (AVG) $MAX + {}^{t}JITdty$ (MIN the MAX = ${}^{t}CK$ (AVG) $MAX \times {}^{t}CL$ (AVG) $MAX \times {}^{t}CL$ |                                                                                          |                                                                                    |                 |                   |

|              | Period jitter                      | <sup>t</sup> JITper                                                                                                                                                                                                                                          | -100                                                                                     | 100                                                                                | ps              | 12                |

|              | Half period                        | <sup>t</sup> JITdty                                                                                                                                                                                                                                          | -100                                                                                     | 100                                                                                | ps              | 13                |

|              | Cycle to cycle                     | <sup>t</sup> JITcc                                                                                                                                                                                                                                           | 200                                                                                      |                                                                                    | ps              | 14                |

| <u>_</u>     | Cumulative error, 2 cycles         | <sup>t</sup> ERR <sub>2per</sub>                                                                                                                                                                                                                             | -150                                                                                     | 150                                                                                | ps              | 15                |

| Clock Jitter | Cumulative error, 3 cycles         | <sup>t</sup> ERR <sub>3per</sub>                                                                                                                                                                                                                             | <b>–</b> 175                                                                             | 175                                                                                | ps              | 15                |

| 옹            | Cumulative error, 4 cycles         | <sup>t</sup> ERR <sub>4per</sub>                                                                                                                                                                                                                             | -200                                                                                     | 200                                                                                | ps              | 15                |

| Š            | Cumulative error, 5 cycles         | <sup>t</sup> ERR <sub>5per</sub>                                                                                                                                                                                                                             | -200                                                                                     | 200                                                                                | ps              | 15, 16            |

|              | Cumulative error,<br>6–10 cycles   | <sup>t</sup> ERR <sub>6–10per</sub>                                                                                                                                                                                                                          | -300                                                                                     | 300                                                                                | ps              | 15, 16            |

|              | Cumulative error,<br>11–50 cycles  | <sup>t</sup> ERR <sub>11–50per</sub>                                                                                                                                                                                                                         | <b>–450</b>                                                                              | 450                                                                                | ps              | 15                |

| =            | DQS output access time from CK/CK# | t DQSCK                                                                                                                                                                                                                                                      | -350                                                                                     | 350                                                                                | ps              | 19                |

| Strobe-Out   | DQS read preamble                  | <sup>t</sup> RPRE                                                                                                                                                                                                                                            | $MIN = 0.9 \times {}^{t}CK$ $MAX = 1.1 \times {}^{t}CK$                                  |                                                                                    | <sup>t</sup> CK | 17, 18,<br>19     |

|              | DQS read postamble                 | <sup>t</sup> RPST                                                                                                                                                                                                                                            | $MIN = 0.4 \times {}^{t}CK$ $MAX = 0.6 \times {}^{t}CK$                                  |                                                                                    | <sup>t</sup> CK | 17, 18,<br>19, 20 |

| Data         | CK/CK# to DQS Low-Z                | <sup>t</sup> LZ <sub>1</sub>                                                                                                                                                                                                                                 | MIN = <sup>†</sup> AC (MIN)<br>MAX = <sup>†</sup> AC (MAX)                               |                                                                                    | ps              | 19, 21,<br>22     |

#### **Table 9: AC Operating Specifications and Conditions (Continued)**

Not all speed grades listed may be supported for this device; refer to the title page for speeds supported; Notes: 1–5 apply to the entire table;

| AC Characteristics Parameter |                                                                  |                              | -2                                                      | 5E                                             |                 |               |

|------------------------------|------------------------------------------------------------------|------------------------------|---------------------------------------------------------|------------------------------------------------|-----------------|---------------|

|                              | Parameter                                                        | Symbol                       | Min                                                     | Max                                            | Units           | Notes         |

|                              | DQS rising edge to CK rising edge                                | <sup>t</sup> DQSS            |                                                         | .25 × <sup>t</sup> CK<br>.25 × <sup>t</sup> CK | <sup>t</sup> CK | 18            |

|                              | DQS input-high pulse width                                       | <sup>t</sup> DQSH            |                                                         | .35 × <sup>t</sup> CK<br>= n/a                 | <sup>t</sup> CK | 18            |

|                              | DQS input-low pulse width                                        | <sup>t</sup> DQSL            |                                                         | $MIN = 0.35 \times {}^{t}CK$ $MAX = n/a$       |                 | 18            |

| e-In                         | DQS falling to CK rising: set-<br>up time                        | <sup>t</sup> DSS             | $MIN = 0.2 \times {}^{t}CK$ $MAX = n/a$                 |                                                | <sup>t</sup> CK | 18            |

| Strobe-In                    | DQS falling from CK rising:<br>hold time                         | <sup>t</sup> DSH             | $MIN = 0.2 \times {}^{t}CK$ $MAX = n/a$                 |                                                | <sup>t</sup> CK | 18            |

| Data                         | Write preamble setup time                                        | tWPRES                       | MIN = 0<br>MAX = n/a                                    |                                                | ps              | 23, 24        |

|                              | DQS write preamble                                               | tWPRE                        | $MIN = 0.35 \times {}^{t}CK$ $MAX = n/a$                |                                                | <sup>t</sup> CK | 18            |

|                              | DQS write postamble                                              | tWPST                        | $MIN = 0.4 \times {}^{t}CK$ $MAX = 0.6 \times {}^{t}CK$ |                                                | <sup>t</sup> CK | 18, 25        |

|                              | WRITE command to first DQS transition                            | -                            | $MIN = WL - {}^{t}DQSS$ $MAX = WL + {}^{t}DQSS$         |                                                | <sup>t</sup> CK |               |

|                              | DQ output access time from CK/CK#                                | <sup>t</sup> AC              | -400                                                    | 400                                            | ps              | 19            |

|                              | DQS–DQ skew, DQS to last<br>DQ valid, per group, per ac-<br>cess | <sup>t</sup> DQSQ            | -                                                       | 200                                            | ps              | 26, 27        |

| Ħ                            | DQ hold from next DQS strobe                                     | <sup>t</sup> QHS             | -                                                       | 300                                            | ps              | 28            |

| Data-Out                     | DQ-DQS hold, DQS to first<br>DQ not valid                        | <sup>t</sup> QH              | $MIN = {}^{t}HP - {}^{t}QHS$ $MAX = n/a$                |                                                | ps              | 26, 27,<br>28 |

|                              | CK/CK# to DQ, DQS High-Z                                         | <sup>t</sup> HZ              | $MIN = n/a$ $MAX = {}^{t}AC (MAX)$                      |                                                | ps              | 19, 21,<br>29 |

|                              | CK/CK# to DQ Low-Z                                               | <sup>t</sup> LZ <sub>2</sub> | $MIN = 2 \times {}^{t}AC (MIN)$ $MAX = {}^{t}AC (MAX)$  |                                                | ps              | 19, 21,<br>22 |

|                              | Data valid output window                                         | DVW                          | $MIN = {}^{t}QH - {}^{t}DQSQ$ $MAX = n/a$               |                                                | ns              | 26, 27        |

#### **Table 9: AC Operating Specifications and Conditions (Continued)**

Not all speed grades listed may be supported for this device; refer to the title page for speeds supported; Notes: 1–5 apply to the entire table;

| AC Characteristics |                                            |      |                   |                                          |     |                 |               |

|--------------------|--------------------------------------------|------|-------------------|------------------------------------------|-----|-----------------|---------------|

|                    | Parameter                                  |      | Symbol            | Min                                      | Max | Units           | Notes         |

|                    | DQ and DM input setup time to DQS          |      | <sup>t</sup> DSb  | 50                                       | -   | ps              | 26, 30,<br>31 |

| _                  | DQ and DM input hold time to DQS           |      | <sup>t</sup> DHb  | 125                                      | -   | ps              | 26, 30,<br>31 |

| Data-In            | DQ and DM input setup time to DQS          |      | <sup>t</sup> DSa  | 250                                      | -   | ps              | 26, 30,<br>31 |

|                    | DQ and DM input hold time to DQS           |      | <sup>t</sup> DHa  | 250                                      | -   | ps              | 26, 30,<br>31 |

|                    | DQ and DM input pulse width                |      | <sup>t</sup> DIPW | $MIN = 0.35 \times {}^{t}CK$ $MAX = n/a$ |     | <sup>t</sup> CK | 18, 32        |

|                    | Input setup time                           |      | <sup>t</sup> ISb  | 175                                      | _   | ps              | 31, 33        |

|                    | Input hold time                            |      | <sup>t</sup> IHb  | 250                                      | _   | ps              | 31, 33        |

|                    | Input setup time                           |      | <sup>t</sup> ISa  | 375                                      | -   | ps              | 31, 33        |

|                    | Input hold time                            |      | <sup>t</sup> IHa  | 375                                      | -   | ps              | 31, 33        |

|                    | Input pulse width                          |      | <sup>t</sup> IPW  | 0.6                                      | -   | <sup>t</sup> CK | 18, 32        |

| ress               | ACTIVATE-to-ACTIVATE de-<br>lay, same bank |      | <sup>t</sup> RC   | 55                                       | -   | ns              | 18, 34,<br>51 |

| and Address        | ACTIVATE-to-READ or WRITE delay            |      | <sup>t</sup> RCD  | 12.5                                     | -   | ns              | 18            |

|                    | ACTIVATE-to-PRECHARGE delay                |      | <sup>t</sup> RAS  | 45                                       | 70K | ns              | 18, 34,<br>35 |

| E                  | PRECHARGE period                           |      | <sup>t</sup> RP   | 12.5                                     | _   | ns              | 18, 36        |

| Command            | PRECHARGE ALL                              | <1Gb | <sup>t</sup> RPA  | 12.5                                     | _   | ns              | 18, 36        |

|                    | period                                     | ≥1Gb | <sup>t</sup> RPA  | 15                                       | -   | ns              | 18, 36        |

|                    | ACTIVATE-to-ACTI-                          | x8   | <sup>t</sup> RRD  | 7.5                                      | -   | ns              | 18, 37        |

|                    | VATE delay different bank                  | x16  | <sup>t</sup> RRD  | 10                                       | -   | ns              | 18, 37        |

|                    | 4-bank activate                            | x8   | <sup>t</sup> FAW  | 35                                       | -   | ns              | 18, 38        |

|                    | period (≥1Gb)                              | x16  | <sup>t</sup> FAW  | 45                                       | _   | ns              | 18, 38        |

#### **Table 9: AC Operating Specifications and Conditions (Continued)**

Not all speed grades listed may be supported for this device; refer to the title page for speeds supported; Notes: 1–5 apply to the entire table;

|              | AC Chara                                           |       |                                 | -25E                                                                   |                                       |                 |               |

|--------------|----------------------------------------------------|-------|---------------------------------|------------------------------------------------------------------------|---------------------------------------|-----------------|---------------|

|              | Parameter                                          |       | Symbol                          | Min                                                                    | Max                                   | Units           | Notes         |

| SS           | Internal READ-to-PRE-<br>CHARGE delay              |       | <sup>t</sup> RTP                | 7.5                                                                    | -                                     | ns              | 18, 37,<br>39 |

| Address      | CAS#-to-CAS#<br>delay                              |       | <sup>t</sup> CCD                | 2                                                                      | -                                     | <sup>t</sup> CK | 18            |

| and          | Write recovery time                                |       | <sup>t</sup> WR                 | 15                                                                     | -                                     | ns              | 18, 37        |

| anda         | Write AP recovery + pre-<br>charge time            |       | <sup>t</sup> DAL                | <sup>t</sup> WR + <sup>t</sup> RP                                      | -                                     | ns              | 40            |

| Command      | Internal WRITE-to-READ de-<br>lay                  |       | <sup>t</sup> WTR                | 7.5                                                                    | -                                     | ns              | 18, 37        |

|              | LOAD MODE cycle time                               |       | <sup>t</sup> MRD                | 2                                                                      | -                                     | <sup>t</sup> CK | 18            |

|              | REFRESH-to-<br>ACTIVATE or to<br>-REFRESH interval | 256Mb | <sup>t</sup> RFC                | 75                                                                     | _                                     | ns              | 18, 41        |

|              |                                                    | 512Mb |                                 | 105                                                                    | _                                     |                 |               |

|              |                                                    | 1Gb   |                                 | 127.5                                                                  | _                                     |                 |               |

|              |                                                    | 2Gb   |                                 | 195                                                                    | _                                     |                 |               |

| ء            | Average periodic refresh (commercial)              |       | <sup>t</sup> REFI               | -                                                                      | 7.8                                   | μs              | 18, 41        |

| Refresh      | Average periodic refresh (industrial)              |       | <sup>t</sup> REFI <sub>IT</sub> | -                                                                      | 3.9                                   | μs              | 18, 41        |

| _            | Average periodic refresh (automotive)              |       | <sup>t</sup> REFI <sub>AT</sub> | -                                                                      | 3.9                                   | μs              | 18, 41        |

|              | Average periodic refresh (automotive)              |       | <sup>t</sup> REFI <sub>UT</sub> | -                                                                      | 0.975                                 | μs              | 18, 41        |

|              | CKE LOW to CK, CK# uncertainty                     |       | <sup>t</sup> DELAY              | MIN limit = ${}^{t}$ IS + ${}^{t}$ CK + ${}^{t}$ IH  MAX limit = $n/a$ |                                       | ns              | 42            |

| hse          | Exit SELF REFRESH to non-<br>READ command          |       | <sup>t</sup> XSNR               | MIN limit = ${}^{t}RFC$ (MIN) + 10<br>MAX limit = $n/a$                |                                       | ns              | 52            |

| Self Refresh | Exit SELF REFRESH to READ command                  |       | <sup>t</sup> XSRD               | MIN limit = 200 tCK MAX limit = n/a                                    |                                       | <sup>t</sup> CK | 18, 52        |

| Self         | Exit SELF REFRESH timing reference                 |       | <sup>t</sup> ISXR               |                                                                        | MIN limit = tIS ps<br>MAX limit = n/a |                 | 33, 43,<br>52 |

#### **Table 9: AC Operating Specifications and Conditions (Continued)**

Not all speed grades listed may be supported for this device; refer to the title page for speeds supported; Notes: 1–5 apply to the entire table;

|            | AC Characteristics                                                     |        |                    | -25E                                                                                 |                   |                 |        |

|------------|------------------------------------------------------------------------|--------|--------------------|--------------------------------------------------------------------------------------|-------------------|-----------------|--------|

|            | Parameter                                                              |        | Symbol             | Min                                                                                  | Max               | Units           | Notes  |

|            | Exit active power- MR12<br>down to READ 0                              |        | <sup>t</sup> XARD  | 2                                                                                    | -                 | <sup>t</sup> CK | 18     |

| Power-Down | command                                                                | MR12 = |                    | 8 - AL                                                                               | -                 | <sup>t</sup> CK | 18     |

|            | Exit precharge power-down and active power-down to any nonREAD command |        | <sup>t</sup> XP    | 2                                                                                    | -                 | <sup>t</sup> CK | 18     |

|            | CKE MIN HIGH/LOW time                                                  |        | <sup>t</sup> CKE   | MIN = 3<br>MAX = n/a                                                                 |                   | <sup>t</sup> CK | 18, 44 |

|            | ODT to power-down entry latency                                        |        | <sup>t</sup> ANPD  | 3                                                                                    | -                 | <sup>t</sup> CK | 18     |

|            | ODT power-down exit laten-<br>cy                                       |        | <sup>t</sup> AXPD  | 8                                                                                    | -                 | <sup>t</sup> CK | 18     |

|            | ODT turn-on delay                                                      |        | <sup>t</sup> AOND  | 2                                                                                    |                   | <sup>t</sup> CK | 18     |

|            | ODT turn-off delay                                                     |        | <sup>t</sup> AOFD  | 2.5                                                                                  |                   | <sup>t</sup> CK | 18, 45 |

| ODT        | ODT turn-on                                                            |        | <sup>t</sup> AON   | $MIN = {}^{t}AC (MIN)$ $MAX = {}^{t}AC (MAX) + 600$                                  |                   | ps              | 19, 46 |

| ō          | ODT turn-off                                                           |        | <sup>t</sup> AOF   | $MIN = {}^{t}AC (MIN)$ $MAX = {}^{t}AC (MAX) + 600$                                  |                   | ps              | 47, 48 |

|            | ODT turn-on<br>(power-down mode)                                       |        | <sup>t</sup> AONPD | $MIN = {}^{t}AC (MIN) + 2000$<br>$MAX = 2 \times {}^{t}CK + {}^{t}AC (MAX) + 1000$   |                   | ps              | 49     |

|            | ODT turn-off<br>(power-down mode)                                      |        | <sup>t</sup> AOFPD | $MIN = {}^{t}AC (MIN) + 2000$<br>$MAX = 2.5 \times {}^{t}CK + {}^{t}AC (MAX) + 1000$ |                   | ps              |        |

|            | ODT enable from MRS com-<br>mand                                       |        | <sup>t</sup> MOD   |                                                                                      | N = 12<br>X = n/a | ns              | 18, 50 |

- Notes: 1. All voltages are referenced to V<sub>SS</sub>.

- 2. Tests for AC timing, I<sub>DD</sub>, and electrical AC and DC characteristics may be conducted at nominal reference/supply voltage levels, but the related specifications and the operation of the device are warranted for the full voltage range specified. ODT is disabled for all measurements that are not ODT-specific.

- 3. Outputs measured with equivalent load (see Figure 2).

- 4. AC timing and I<sub>DD</sub> tests may use a V<sub>II</sub>-to-V<sub>IH</sub> swing of up to 1.0V in the test environment, and parameter specifications are guaranteed for the specified AC input levels under normal use conditions. The slew rate for the input signals used to test the device is 1.0 V/ns for signals in the range between  $V_{IL(AC)}$  and  $V_{IH(AC)}$ . Slew rates other than 1.0 V/ns may require the timing parameters to be derated as specified.

- 5. The AC and DC input level specifications are as defined in the SSTL 18 standard (that is, the receiver will effectively switch as a result of the signal crossing the AC input level and will remain in that state as long as the signal does not ring back above [below] the DC input LOW [HIGH] level).

- 6. CK and CK# input slew rate is referenced at 1 V/ns (2 V/ns if measured differentially).

- 7. Operating frequency is only allowed to change during self refresh mode (see Figure 1), precharge power-down mode, or system reset condition (see Reset). SSC allows for small deviations in operating frequency, provided the SSC guidelines are satisfied.

- 8. The clock's <sup>t</sup>CK (AVG) is the average clock over any 200 consecutive clocks and <sup>t</sup>CK (AVG) MIN is the smallest clock rate allowed (except for a deviation due to allowed clock jitter). Input clock jitter is allowed provided it does not exceed values specified. Also, the jitter must be of a random Gaussian distribution in nature.

- Spread spectrum is not included in the jitter specification values. However, the input clock can accommodate spread spectrum at a sweep rate in the range 8–60 kHz with an additional one percent <sup>t</sup>CK (AVG); however, the spread spectrum may not use a clock rate below <sup>t</sup>CK (AVG) MIN or above <sup>t</sup>CK (AVG) MAX.

- 10. MIN (<sup>t</sup>CL, <sup>t</sup>CH) refers to the smaller of the actual clock LOW time and the actual clock HIGH time driven to the device. The clock's half period must also be of a Gaussian distribution; <sup>t</sup>CH (AVG) and <sup>t</sup>CL (AVG) must be met with or without clock jitter and with or without duty cycle jitter. <sup>t</sup>CH (AVG) and <sup>t</sup>CL (AVG) are the average of any 200 consecutive CK falling edges. <sup>t</sup>CH limits may be exceeded if the duty cycle jitter is small enough that the absolute half period limits (<sup>t</sup>CH [ABS], <sup>t</sup>CL [ABS]) are not violated.

- 11. <sup>†</sup>HP (MIN) is the lesser of <sup>†</sup>CL and <sup>†</sup>CH actually applied to the device CK and CK# inputs; thus, <sup>†</sup>HP (MIN) ≥ the lesser of <sup>†</sup>CL (ABS) MIN and <sup>†</sup>CH (ABS) MIN.

- 12. The period jitter (<sup>t</sup>JITper) is the maximum deviation in the clock period from the average or nominal clock allowed in either the positive or negative direction. JEDEC specifies tighter jitter numbers during DLL locking time. During DLL lock time, the jitter values should be 20 percent less those than noted in the table (DLL locked).

- 13. The half-period jitter (<sup>t</sup>JITdty) applies to either the high pulse of clock or the low pulse of clock; however, the two cumulatively can not exceed <sup>t</sup>JITper.

- 14. The cycle-to-cycle jitter (<sup>t</sup>JITcc) is the amount the clock period can deviate from one cycle to the next. JEDEC specifies tighter jitter numbers during DLL locking time. During DLL lock time, the jitter values should be 20 percent less than those noted in the table (DLL locked).

- 15. The cumulative jitter error (terror, where n is 2, 3, 4, 5, 6–10, or 11–50 is the amount of clock time allowed to consecutively accumulate away from the average clock over any number of clock cycles.

- 16. JEDEC specifies using <sup>t</sup>ERR<sub>6-10per</sub> when derating clock-related output timing (see notes 19 and 48). Micron requires less derating by allowing <sup>t</sup>ERR<sub>5per</sub> to be used.

- 17. This parameter is not referenced to a specific voltage level but is specified when the device output is no longer driving (tRPST) or beginning to drive (tRPRE).

- 18. The inputs to the DRAM must be aligned to the associated clock, that is, the actual clock that latches it in. However, the input timing (in ns) references to the <sup>t</sup>CK (AVG) when determining the required number of clocks. The following input parameters are determined by taking the specified percentage times the <sup>t</sup>CK (AVG) rather than <sup>t</sup>CK: <sup>t</sup>IPW, <sup>t</sup>DIPW, <sup>t</sup>DQSS, <sup>t</sup>DQSH, <sup>t</sup>DQSL, <sup>t</sup>DSS, <sup>t</sup>DSH, <sup>t</sup>WPST, and <sup>t</sup>WPRE.

- 19. The DRAM output timing is aligned to the nominal or average clock. Most output parameters must be derated by the actual jitter error when input clock jitter is present; this will result in each parameter becoming larger. The following parameters are required to be derated by subtracting terms, the following parameters are required to be derated by subtracting the following parameters are required to be derated by subtracting terms, the following parameters are required to be derated by subtracting terms, the following parameters are required to be derated by subtracting terms, the following parameters are required to be derated by subtracting terms, the following parameters are required to be derated by subtracting terms, the following terms that terms that following terms, the following terms that the fol

- 20. When DQS is used single-ended, the minimum limit is reduced by 100ps.

- 21. <sup>t</sup>HZ and <sup>t</sup>LZ transitions occur in the same access time windows as valid data transitions. These parameters are not referenced to a specific voltage level, but specify when the device output is no longer driving (<sup>t</sup>HZ) or begins driving (<sup>t</sup>LZ).

- 22. <sup>t</sup>LZ (MIN) will prevail over a <sup>t</sup>DQSCK (MIN) + <sup>t</sup>RPRE (MAX) condition.

- 23. This is not a device limit. The device will operate with a negative value, but system performance could be degraded due to bus turnaround.

- 24. It is recommended that DQS be valid (HIGH or LOW) on or before the WRITE command. The case shown (DQS going from High-Z to logic LOW) applies when no WRITEs were previously in progress on the bus. If a previous WRITE was in progress, DQS could be HIGH during this time, depending on <sup>t</sup>DQSS.

- 25. The intent of the "Don't Care" state after completion of the postamble is that the DQS-driven signal should either be HIGH, LOW, or High-Z, and that any signal transition within the input switching region must follow valid input requirements. That is, if DQS transitions HIGH (above V<sub>IH[DC]min</sub>), then it must not transition LOW (below V<sub>IH[DC]</sub>) prior to <sup>†</sup>DOSH (MIN).

- 26. Referenced to each output group: x8 = DQS with DQ[7:0]; x16 = LDQS with DQ[7:0]; and UDQS with DQ[15:8].

- 27. The data valid window is derived by achieving other specifications: <sup>†</sup>HP (<sup>†</sup>CK/2), <sup>†</sup>DQSQ, and <sup>†</sup>QH (<sup>†</sup>QH = <sup>†</sup>HP <sup>†</sup>QHS). The data valid window derates in direct proportion to the clock duty cycle and a practical data valid window can be derived.